| |  | | Pagina creata il 01/06/2012 [5070 giorni fa] |

|

Applicazioni Software

|

PROGETTO n° 15 - 1/6

[145 di 189]

|

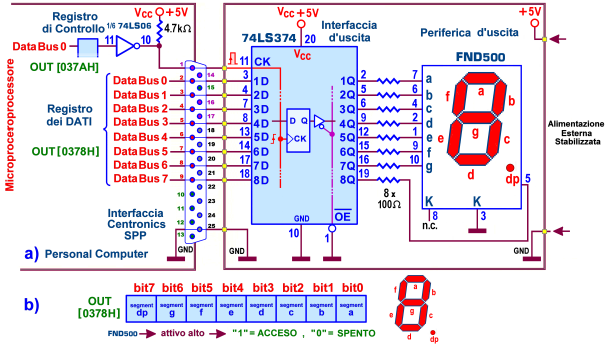

La periferica coinvolta nel progetto (un Digit a Catodo

comune di tipo FND500)

sfrutta comunque l'energia del componente che la pilota; nella versione

trattata in queste pagine il progetto si avvale della

memoria esterna 74LS374,

alimentata esternamente con un piccolo alimentatore da 5 volt stabilizzati e

collegata direttamente in uscita alla porta parallela; si tratta di una

batteria di 8 Flip-Flops D-Type, le cui linee d'uscita

(di tipo buffer 3-state non invertente, rese sempre attive dalla presenza

del segnale di abilitazione, Out Enable, (OE,

attivo basso) permanentemente collegato a massa) sono chiamate ad alimentare

gli 8 led del digit, attraverso altrettanti resistori

da 100 Ohm: questa

precauzione è sostanzialmente inutile, dato che la tensione residua in

uscita (al netto della caduta di tensione interna) si avvicinerà comunque a

quella di un diodo LED Rosso in zona di

funzionamento (circa 1,8V).

Per questa ragione il resistore potrebbe anche essere omesso, pur

consapevoli che in queste condizioni la singola uscita TTL sarà costretta ad

erogare corrente decisamente superiore a quella prevista (0,4mA)

nel suo normale funzionamento logico, anche se questo non le nuocerà più di

tanto.

La parte b) dello schema mostra la Tabella di Associazione

Logica: il suo contenuto propone la configurazione del byte da porre

sulla porta d'uscita, specificando (per ciascuno dei suoi 8 bit) sia il

livello attivo che il segmento ad esso associato; questa disponibilità

virtualizza la presenza del digit,

offrendo ogni dettaglio utile alla creazione del programma necessario per la

sua gestione, cioè senza dover analizzare lo schema elettronico ad esso

relativo, anche se la persona chiamata a progettare il codice non è la

stessa che ha progettato il circuito; si tratta proprio della struttura

ideale per costruire una tabella di conversione

in grado di associare a ciascun simbolo la corrispondente codifica a

8 bit.

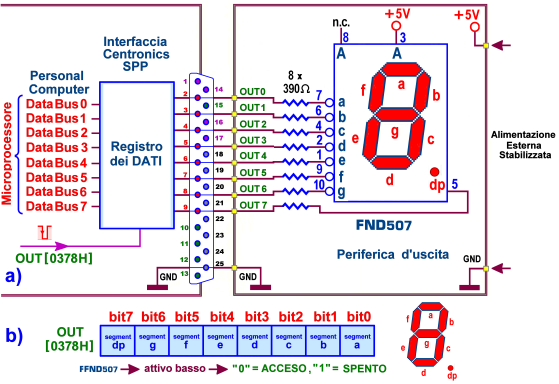

Una possibile variante si propone di alimentare il Digit

FND550 direttamente attraverso i pin 2÷pin

9 del connettore della porta parallela,

rinunciando alla presenza della

memoria esterna 74LS374;

se, come in questo caso, ci si deve occupare di un solo digit, essa è

effettivamente ridondante e il servizio richiesto può essere garantito anche

direttamente dalla porta dati 0378H

della parallela.

Per questo progetto vale la stessa Tabella di

Associazione Logica e lo stesso codice gestionale descritto per

quello precedente, nel quale le 5 istruzioni che agiscono sul registro di

controllo 037AH, pur eseguite regolarmente,

sono ora ovviamente ininfluenti e comunque possono tranquillamente essere

tolte dal codice..

Pur con le note perplessità legate al fatto di costringere la LPT ad erogare

corrente verso una periferica .. assatanata di corrente, rimane positivo il

fatto che in questo caso non è necessaria alcuna alimentazione esterna.